CYPRESS中国区***(香港齐芯科技有限公司)

CY7C64713-128AXC特点:

功能描述CY7C64713 - 128AXC是一个全静态设计,支持时钟频率高达350兆赫。产生的信号和retimed片上,以确保四个输出***的***低偏移。两个***的LVPECL兼容的时钟输入提供。此功能支持冗余差分时钟源。此外,CY7C64713 - 128AXC支持单端的LVCMOS时钟分配系统。四个输出***每一个都可以单独提供的2.5V或3.3V,支持混合电压应用。选择的FSELx引脚之间的输入参考频率划分由一个或两个。该分频器可设置为每个单独的输出***。在CY7C64713 - 128AXC输出***在highCimpedance状态解除报警的温仁才由引脚。声称将在温仁才使输出***。请参阅第4页的详细信息,输出HighCImpedance控制表。输出可同步停止(逻辑低状态)。提供的产出能力的LVCMOS兼容程度,推动终止50Ω传输线路。对于系列终止输电线路,对CY7C64713 - 128AXC输出每个人都可以驱动一个或两个痕迹给予了1:32的设备在VCC = 3.3V的有效扇出。该器件采用7x7平方毫米封装,48引脚LQFP封装。

CY7C64713-128AXC(***)***大额定值:

手动复位输入许多微处理器为基础的产品需要手动复位capabil知音,使运营商,测试技术人员,或外部逻辑电路来启动复位。甲先生为逻辑低,serts复位。虽然他仍然断言复位低,主动为复位超时周期(激进党)致辞后返回高。这种输入有一个内部20kΩ的上拉电阻,因此它可以在公开,如果不使用它。议员可驱动具有TTL或CMOS逻辑电平,或开漏/集电极输出。连接一个常开的MR瞬时开关至GND,以创造一个手动复位功能,外部去抖电路不需要。如果议员是由长电缆或驱动装置是用在嘈杂的环境,从议员连接0.1μF电容到地提供了额外的噪声***力。

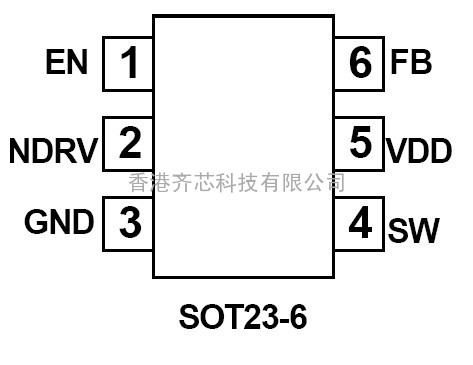

CY7C64713-128AXC引脚说明: 完整的闭环电流控制的同步旋转磁场定向帧(使用转子角观察员)闭环速度控制速度估计可配置参数(PI控制器的收益,有价证券***限额范围内输出,电流反馈扩大器,PWM载波频率为基础计算)为适应不同永磁电机内置为启动传感器控制逻辑,斜坡,在启动和运行与配置的转矩电流限制,条件自动重试(可编程)模拟参考输入(可用于高速参考)RS232C/RS422参考输入全部动态制动直流母线电压的限制逐周期控制开/关控制制动IGBT的损失***小化空间矢量PWM的死区时间插入内建两个IR2175电***应IC接口相损耗,过流(GATEKILL输入),过压,欠压,***保护低成本串行12位A / D转换接口与复用器和样品/保持电路可选逆变腿(偏低)在IR2175电***应集成电路代替4路模拟输出(脉宽调制)对内部数据的EEPROM启动初始化本地/通过主机参数寄存器接口AT24C01A,128X8通用主机通信接口RS232C或RS422主机接口快速SPI从主机接口与多点能力的并行主机接口(共12针)复用数据/地址总线地址使能研发/西铁离散I / O,以***模式运作STARTSTOP (输入)埃斯托普(输入)

CY7C64713-128AXC Features:

Functional Description The CY7C64713-128AXC is a full static design supporting clock frequencies up to 350 MHz. The signals are generated and retimed on-chip to ensure minimal skew between the four output banks. Two independent LVPECL compatible clock inputs are ***ailable. This feature supports redundant differential clock sources. In addition, the CY7C64713-128AXC supports single-ended LVCMOS clock distribution systems. Each of the four output banks can be individually supplied by 2.5V or 3.3V, supporting mixed voltage applicati***. The FSELx pins choose between division of the input reference frequency by one or two. The frequency divider can be set individually for each output bank. The CY7C64713-128AXC output banks are in highCimpedance state by deasserting the OEN pins. Asserting OEN will the enable output banks. Please see the Output HighCImpedance Control table on page 4 for details. The outputs can be synchronously stopped (logic low state). The outputs provide LVCMOS compatible levels with the capability to drive terminated 50 Ω tran***ission lines. For series terminated tran***ission lines, each of the CY7C64713-128AXC outputs can drive one or two traces giving the devices an effective fanout of 1:32 at VCC = 3.3V. The device is packaged in a 7x7 mm2 48-lead LQFP package.

CY7C64713-128AXC(Absolute) Maximum Ratings:

Manual Reset Input Many µP-based products require manual reset capabil- ity, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic low on MR as- serts reset. Reset remains asserted while MR is low, and for the Reset Active Timeout Period (tRP) after MR returns high. This input has an internal 20kΩ pull-up resistor, so it can be left open if it is not used. MR can be driven with TTL or CMOS-logic levels, or with open-drain / collector outputs. Connect a normally open momentary switch from MR to GND to create a manual-reset function; external debounce circuitry is not required. If MR is driven from long cables or if the device is used in a noisy environment, connecting a 0.1µF capacitor from MR to ground provides additional noise immunity.

CY7C64713-128AXC Pinout: Complete closed loop current control based on Synchronously Rotating Frame Field Orientation (using Rotor Angle Observer) Closed loop velocity control based on estimated speed Configurable parameters (PI controller gains, PI output limit range, current feedback scaling, PWM carrier frequency) provide adaptation to various PM motors Built-in Sensorless control logic for start-up, ramping, and running conditi*** Auto Retry (programmable) on start-up with configurable torque current limit Analog reference input (can be used for speed reference) RS232C/RS422 reference input Full dynamic braking control for DC bus voltage limitation Cycle-by-cycle on/off Control for Brake IGBT Loss minimization Space Vector PWM with deadtime insertion Build-in two IR2175 current sensing IC interfaces Phase Loss, Overcurrent (GATEKILL input), Overvoltage, Undervoltage, Overspeed protection Low cost serial 12bit A/D interface with multiplexer and sample/hold circuit Optional Inverter Leg (low side) current sensing in lieu of IR2175 IC 4 channel analog output (PWM) Local EEPROM for startup initialization of internal data/parameters through host register interface AT24C01A, 128X8 Versatile host communication interface RS232C or RS422 host interface Fast SPI sl***e host interface with multi-drop capability Parallel Host interface (total 12 pins) Multiplexed data/address bus Address Enable RD/WR Discrete I/Os for Standalone mode operation STARTSTOP (Input) ESTOP (Input)