本公司***销售大型进口各种品牌DCS系统模块备件:BENTLY NEVADA3500/3300,AB,ABB Advant OCS,ABB MOD 30/MODCELL,ABB MOD 300,ABB Bailey INFI 90,ABB Procontic,ABB Procontrol,Rosemount RS-3,Yokogawa Centum XL,Yokogawa microXL,FOXBORO I/A,Westinghouse,Ovation,Honeywell QCS,Honeywell TDC系列,Honeywell S9000,HITACHI,Mitsubishi PLC,Motorola MVME,ALSTOM MVME,Other VME,TOSHIBA,HP,Yaskawa,FANUC等大型模组,有着充足的库存,交货期快,查询。

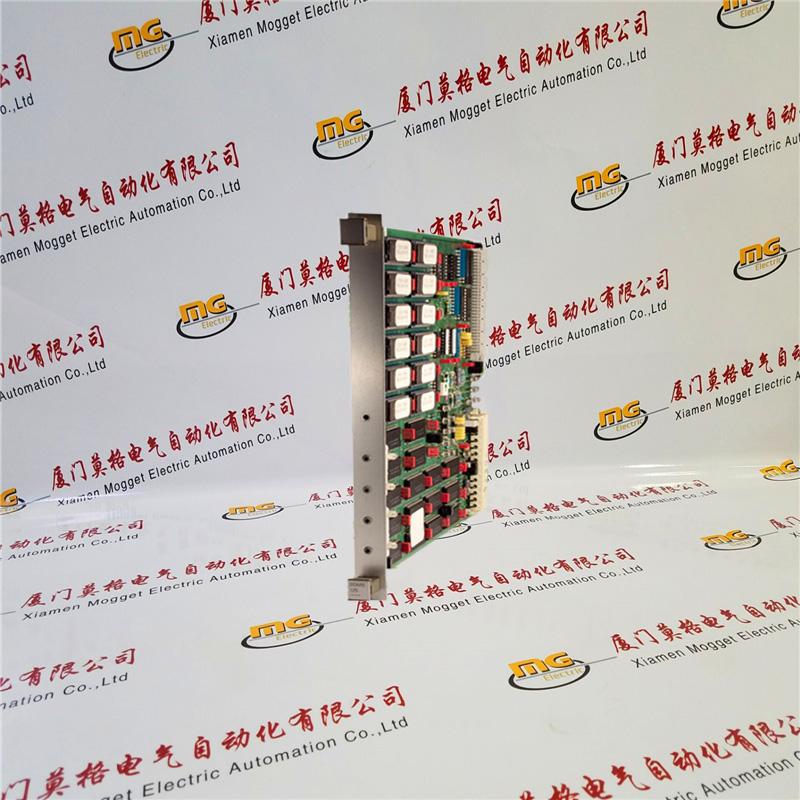

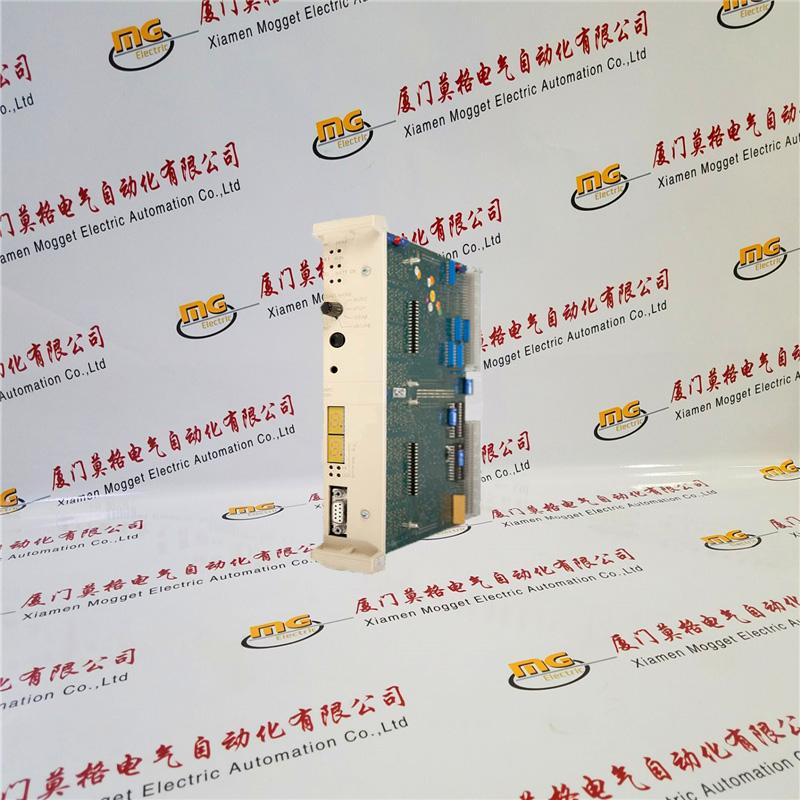

GE IS200TBCIH1B

GE IS200TBCIH1B

GE IS200TBCIH1B

提要

本应用指南介绍了在 VirtexTM-4 器件中实现存储器接口的直接时钟控制数据采集技术。直接时钟控制方案利用了 Virtex-4 系列所独有的某些架构特性(例如,每个 I/O 模块 (IOB) 中均具备一个 64-tap 的***延迟线)。

简介

大多数存储器接口都是源同步接口,从外部存储器器件传出的数据和时钟/ 选***冲是边沿对齐的。在 Virtex-4 器件采集这一数据,需要延迟时钟/ 选***冲或数据。利用直接时钟控制技术,数据经延迟,并与内部 FPGA 时钟实现中心对齐。在这个方案中,内部 FPGA 时钟采集传出的数据。存储器传出的时钟/ 选***冲用于决定与数据位相关的延迟值。因此,与选***冲相关的数据位的数量不受限制。由于无需将选***冲分配给相关数据位,所以不需要其他时钟资源。

时钟/ 选***冲和数据位使用的 Virtex-4 资源是一条 64-tap ***延迟线。该 64-tap ***延迟线可利用 IDELAY 和 IDELAYCTRL primitive 实现。时钟/ 选***冲和数据位均通过此 64-tap***延迟线来布线。虽然选***冲不

用于采集数据,但它用于确定数据与内部 FPGA 时钟实现中心对齐所需的 tap 数量。以下部分将详细解释直接时钟控制技术方案的设计及实现。

选***冲边沿检测

与时钟/ 选***冲相关的数据位的延迟值就是内部 FPGA 时钟上升沿与时钟/ 选***冲中心之间的相位差。假设时钟/ 选***冲和数据实现了边沿对齐。要确定这个相位差,时钟/ 选***冲通过 IOB 内的 64-tap ***延迟线输入,并利用内部 FPGA 时钟在增量 tap 输出端对其进行采样。

要确定时钟/ 选***冲的中心,至少需要检测到时钟/ 选***冲的两个边沿或转换。检测出第二次转换所需的 tap 数(即第二个边沿的 tap)和检测出***次转换所需的 tap 数(即***个边沿的 tap)之差,即为时钟/ 选***冲宽度。这个差值的二分之一就是脉冲中心(即脉冲中心的 tap)。从内部 FPGA 时钟上升沿到时钟/ 选***冲中心之间的 tap 数,即为***个边沿的tap 数与脉冲中心的 tap 数之和。

图1 说明了通过使数据延迟相应的 tap 数,让数据与内部 FPGA 时钟实现中心对齐的两种情况。第 1 种情况所示为,由于时钟/ 选***冲的下降沿是被检测到的***个边沿,因此内部FPGA 时钟的上升沿位于延迟数据的中心。第 2 种情况所示为,由于时钟/ 选***冲的上升沿是检测到的***个边沿,因此内部 FPGA 时钟下降沿位于延迟数据的中心。

通过使数据延迟相应的 tap 数,让数据与内部 FPGA 时钟实现中心对齐的两种情况

实现选***冲边沿检测

由于具有专用的 IDELAY 和 IDELAY_CTRL 电路,所以可以轻松地在 Virtex-4 器件中实现确定延迟值的电路。实现确定延迟值电路的结构图如图2 所示。

实现确定延迟值电路的结构图

利用一个简单的算法检测存储器时钟/ 选***冲的边沿。将初始值为 0 的时钟/ 选***冲输入IDELAY 模块。时钟/ 选***冲将不停地增加 1 tap 的延迟,直到检测到***个边沿。然后记录下检测出***个边沿所需的 tap 数。在检测到第二个边沿之前,时钟/ 选***冲仍然不停地增加 1 tap 的延迟。然后记录下检测出第二个边沿所需的 tap 数。根据两次记录的值,计算出脉冲宽度。在用 tap 数确定时钟/ 选***冲宽度后,除以 2 即得到中间值。中间值与检测出***个边沿所需的 tap 数之和为延迟数据所需的 tap 数。

IDELAY 模块可用的 tap 总数为64。因此,当频率为 200 MHz 或以下时,将无法检测出两个边沿。如果在 64 tap 结束后仅检测出一个边沿,那么延迟数据所需的 tap 数应为,检测出***个边沿所需的 tap 数减去 16 tap (约 1.25 ns,每个 tap 的***约为 75 ps)。一个 200 MHz 时钟/ 选***冲周期的四分之一约为 16 tap。根据时序分析,该值也适用于更低的频率,***低可达 110 MHz。当频率低于 110 MHz 时,如果在 64 tap 结束后未检测出任何边沿,那么延迟数据所需的 tap 数应为 32 tap(约 2.5 ns,每个 tap 的***约为 75 ps)。该值足以使内部 FPGA时钟边沿位于数据窗口内。

检测***个和第二个边沿仅需一个小型状态机。只有在为确定数据延迟 tap 数而发出的虚读操作过程中,才启用该状态机。在正式工作之前,发送至外部存储器器件的虚读操作命令包含多条背靠背读命令。状态机将控制输入 IDELAY 电路的信号,即DLYRST、DLYCE 和 DLYINC。

DLYRST - 延迟线复位信号,将延迟线中的 tap 数重设为按 IOBDELAY_VALUE 属性设置的值。本设计中被设为 "0"。

6ES5308-3UC21

MDS60A0040-5A3-4-00

6ES5 928-3UA21

6ES5 955-3LC13

6ES5 955-3L12

MOVIRET 380

DV6-340-5K5 DV63405K5 -OVP-

6ES5 955-3LC14

6AA6 500-0BC

6SN1123-1AB00-0AA2

80AR 36D4.2QM-W61-BR

PSF 722 EPH07/22/15 CM112M/KTY/VR/AS1H/***50

R77 DY112L/B/TH

MSK 071D-0300-NN-M1-UG1-NNNN

MCA13141-RSOBO-A19N-ST5S00N-R0S0

GFL05-2MSAK100C12/MDFMABR I=20,286

Ersatzteil MSK-IG3

MDD093C-N-030-N2L-130G4

Motor - MPL-B330P-MJ22AA

TG-40-55 / 30533

G-200 2BH1 1640-7GH36 4,4KW/ 50Hz

EM 01.0160.8.222.04.0.0.1

1FT6084-8AH71-3ALO-Z

1 FT5076-0AC01-2-Z

NBT2/25-200 U5A-W4-38/300

MAC 090C-1-GD-4-C/110-A-1/WI515LX5/S005

MAC063A-0-RS-3-C/095-B-0/S001

MAC071A-0-0S-3-C/095-B-0/S001

1FK7064-7AF71-1SB0

NM011BY