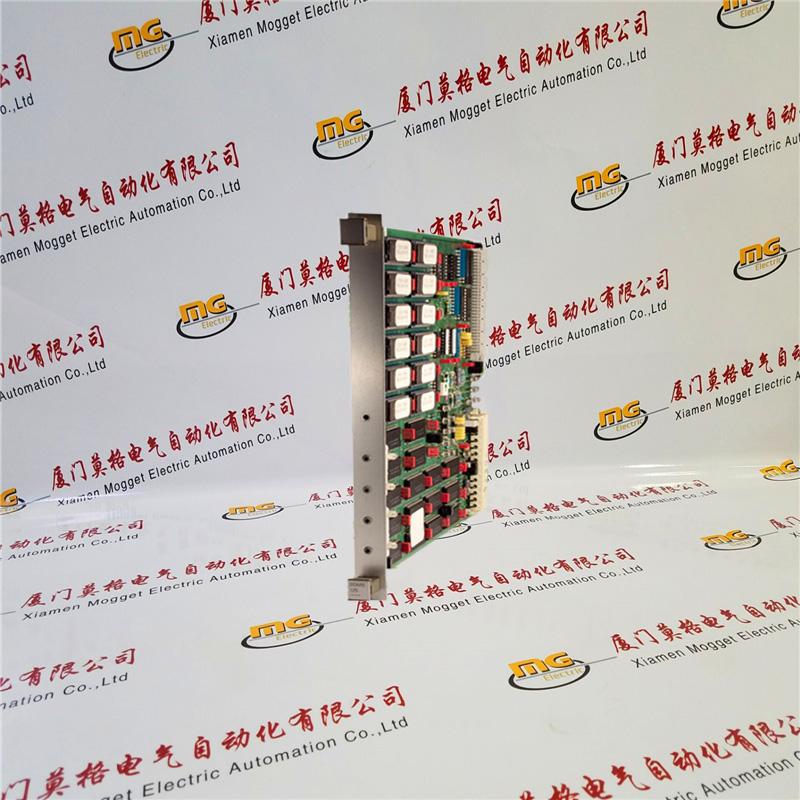

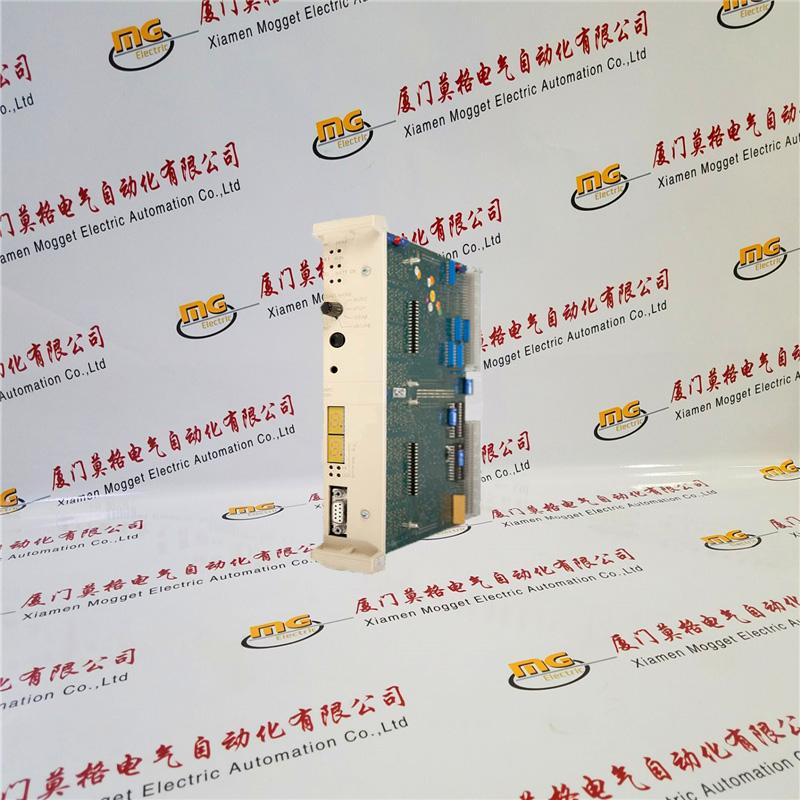

ABB DCS 附件SB808F TK807F

ABB DCS 附件SB808F TK807F

ABB DCS 附件SB808F TK807F

公司销售AB、ABB、GE FANUC、福克斯波罗、英维思、ICS、、本特利、西屋、巴赫曼、艾默生EPRO、施耐德莫迪康、安川、横河、博世力士乐、伍德沃德、摩托罗拉、XYCOM等PLC模块、DCS备件。

应用于以下行业:发电厂DCS监控系统、智能平钢化炉系统制造、PLC可编程输送控制系统、DCS集散控制系统、电器控制系统、造纸、印染生产线、变电站综合自动化控制系统。

为了提高数据的交换能力,有些双口RAM采用信令交换逻辑来通知对方。IDT7130(1K容量)就是采用中断方式交换信令。利用两个特殊的单元(3FFH和3FEH)作为信令字和中断源。假设左端CPU向3FFH写入信令,将由写信号和地址选通信号触发右端的中断输出,只有当右端的CPU响应中断并读取3FFH信令字单元,其中断才被双口RAM撤消。

; 以上是双口RAM自身提供的仲裁逻辑控制,也可采用自行设计的仲裁协议。下面的实例将介绍这种方法。

2.FIFO的工作原理

FIFO(First In First Out)全称是***先出的存储器。***先出也是FIFO的主要特点。

20世纪80年代早期,FIFO芯片是基于移位寄存器的中规模逻辑器件。容量为n的这种FIFO中,输入的数据逐个寄存器移位,经n次移位才能输出。因此,这种FIFO的输入到输出***与容量成正比,工作效率得到限制。

为了提高FIFO的容量和减小输出***,现在FIFO内部存储器均采用双口RAM,数据从输入到读出的延迟大大缩小。以通用的IDT7202为例,结构框图如图4所示。输入和输出具有两套数据线。***的读写地址指针在读写脉冲的控制下顺序地从双口RAM读写数据,读写指针均从***个存储单

元开始,到***后个存储单元,然后,又回到***个存储单元。标志逻辑部分即内部仲裁电路通过对读指针和写指针的比较,相应给出双口RAM的空(EF)和满(FF)状态指示,甚至还有中间指示(XO/HF)。如果内部仲裁仅提供空和满状态指示,FIFO的传输效率得不到充分的艇。新型的FIFO提供可编程标志功能,例如,可以设置空加4或满减4的标志输出。目前,为了使容量得到更大提高,存储单元采用动态RAM代替静态RAM,并将刷新电路集成在芯片,且内部仲裁单元决定器件的输入、读出及自动刷新操作。

IDT7202 结构框图

FIFO只允许两端一个写,一个读,因此FIFO是一种半共享式存储器。在双机系统中,只允许一个CPU往FIFO写数据,另一个CPU从FIFO读数据。而且,只要注意标志输出,空指示不写,满指示不读,就不会发生写入数据丢失和读出数据无效。

3.其他多端口存储器

以上只介绍了两种双端口存储器。随着电子工艺的飞速发展,出现了三端口及以上的存储器,并且在存储深度和宽度上得到很大发展,仲裁逻辑控制更加复杂;但多端口存储器源彼双端口存储器,基本更加复杂;但多端口存储器源自双端口存储器,基本工作原理入双端口存储器相似,这里不一一详述。

二、双口RAM实现数据采集系统

数字信号处理器(DSP)能实时快速地实现各种数字信号处理算法,而DSP的控制功能不强,可以采用8051单片机控制数据采集板,将采集的原始数据送给DSP处理并将处理结果传送给8位单片机。图5给出了利用1片数字信号处理器TMS320F206(以下简称DSP)和2片AT89C51单片机(以下简称MCU)构成多机数据采集系统接口图。

多机数据采集系统接口图

本系统采用两片CMOS静态双口RAM(IDT7132)实现MCU和DSP的数据双向传递。双口RAM作为DSP的片外数据存储器,即用外部数据存储器选通信号DS和高位地址信号经高速或门输出选通双口RAM的片选信号。这样可以利用DSP的重复操作指令(RPT)和数据存储器块移动指令(BLDD)减少数据传送时间,双口RAM的8位数据总线接在DSP的低8位。IDT7132的仲裁逻辑控制只提供Busy逻辑输出,而由于MCU无Busy功能,只能采用自行设计的软件协议仲裁方法。将双口RAM划分为两块:上行数据区(DSP接收MCU采集的数据区)和下地数据区(DSP输出处理结果区)。此处的上行数据区将远大于下行数据区。采用DSP的4个I/O口与MCU中断口和I/O口相连,并在数据区中规定一个信令交换单元。以DSP采集右端MCU上行数据为例,说明仲裁流程。

756-BA2

1492-H6

SC-1N

SS302H-3-D5

SS302H-3Z-D3

SS303H-1Z-D2

NVS4114-0009D

DSQC661 3HAC 026253-00

140ACI03000

MA-0185-100

1756-OB32/A

CIMR-JA2A0004BAA

CIMR-JA2A0006BAA

CIMR-JA2A0020BAA

140ACI04000

140CHS11000

140DDO35300

37-5319

KHDG4V 3 02 157451 21

KHDG5V-7-2C200N -X-VM-U1-H120

IC697ALG440

140ACI04000

140CPS11420

CABA1

PROTEUS/0100C110

2711P-RP1X

PAC/5A/4-20MA

RI41-0/360ES 21CA-2-15S-5-S02

6ES7623-1DE01-0AE3

NT8B27JAAA

6ES5466-4UA11

2711-K10G16

2711P-RAT15

2711-T10C10

MP75A4R

E-64HR

MPG-4

1FK7034-5AZ91-1ZZ9-Z

1746-BAS

1746-NI16I

1746-NO4I

1746-OW16

1746-P1

1746-P2

1747-L553

PP836

PP865

RL-1600

RL-3200

RLE-800

1C31234G01

640D0062H01

640D0190H01

1336F-B030-AA-EN-HAS2-L5E-6M1

1336F-B050-AA-EN-HAS2-GM1-L5E

1336F-BRF150AA-EN-HAS2-L5E

1336F-BRF75-AA-EN-HAS2-L5

140CRA93100

140CRP93100

TSXDEY32D2K

TSXDSY16T2

TSXDSZ32R5

TSXMBP100

TSXP57104M

1756-A7

1756-BA1

1756-CP3

1756-IF6I

1756-IR6I

1756L55M13

1756-OF4

1756-PA72

4808

SR750-P5-G5-D5-HI-A20-R-E

140ACI04000

140ARI03010

140DD035300

140DDI35300

161701-USB

CIMR-AB4A0088 37KW

SGDM-20ADA

J761-003A

J761-004A

1747-L552

1794-ADN

1794-IE4XOE2

1794-IV16

1794-OB16

IC670ALG230

TWDAMI2HT

TWDDDI16DT

TWDLCAA24DRF

1394C-SJT10-T

STI 80-310

1131B

IC693CPU363

6ES5417-7AA21

JANCD-NIF01-1

JANCD-NIO01-1

JANCD-NTU01-1

JZNC-NRK01-1

JZRCR-NTU01D-1

SGDR-COA040A01B

SGDR-EA1400N

00-100-026

SIEMENS OP7 6***3607-1JC20-0AX0

RFX600A

1C31205G01

1756-RM

1794-IRT8

1769-PA2

6ES7335-7HG01-0AB0

6SL3000-0BE31-2AA0

AS-P890-000

1336S-B020-AA-EN4

1606-XLP

140ACIO4000

6***66480AC113AX0

6ES5103-8MA03

6SE7022-6EC61

6SE7022—7EP60

1756-PA75/B

SGM-08A3FJ62

VE3002

VE5001

6FC5247-0AA30-0AA0

6ES5314-3UA11

6ES5466-4UA11

BCH0801O22A1C

BCH0802O22A1C

BCH1301M22A1C

LXM23AU04M3X

LXM23AU07M3X

DPW01

140CPU65150

PCA66

PCX20-CXB

1756CNB

1756-IB16I

1756-IF16

IC610CHS110A

1756-L62

TDS2022

3601E

KBLM6180GD-CM

6***6643-0CD01-1AX1

6ES7214-1AE30-0XB0

6ES7214-2AD23-0XB8

6ES7221-1BH30-0XB

6ES7223-1BH30-0XB0

6ES7223-1BL30-0XB0

RXD63B200

1746-A7

1746-IB16

1746-NI8

1746-NO4I

1746-OW16

1746-P4

1747-L532

DCP10

DDI01

DLM02

MDV60A0110-5A3-4-00

1746-IB32

1746-NIO4I

1746-NT4

1746-OB32

PC832-001-T

IC697CH5790

250B-1-A

1C31234G01

TX4000

S1936D

TX4000

2094-BM03

2094-BM03-S

140ACI03000

140AMM09000

140CPS21400

140CPU65150

140DDI35300

AM-SA85-000

TSXAEY1600

TSXDEY32D2K

TSXP573634M

XBTF024610

140DAI75300

1756-0B16

1756-0F4

1756-A10

1756-CNB

1756-DHRIO

1756-DNB

1756-ENBT

1756-IB32

1756-IF8

1756-L61

1756-PA72

3HAC7998-1

VX4101A

1305-BA03A-HA2

1784-PCIC

WATLOW ANAFAZE CLS208

PCA66

PCX20-CXB

1756-L62/B

6ES7 151-1AA03-0AB0

6ES7 141-1FB12-0XB0

6ES7 144-1FB31-0XB0

6ES7 148-1DA00-0XA0

45UV5-1009

6ES71531AA030XB0

6ES73135BF030AB0

6ES73152AH140AB0

6ES73211BL000AA0

6ES73221BL000AA0

6ES73231BL000AA0

6ES73311KF020AB0

6ES73325HD010AB0

6ES73501AH030AE0

6ES79538LG200AA0

6ES79720BA120XA0

6ES79720CB200XA0

140CPU6515O

140CRP93200

140DDI35300

140DDO35300

140NOE77100

140NOM21200

PTQ-PDPMV1

6ES71531AA030XB0

6ES73135BF030AB0

6ES73152AH140AB0

6ES73211BL000AA0

6ES73221BL000AA0

6ES73231BL000AA0

6ES73311KF020AB0

6ES73325HD010AB0

6ES73501AH030AE0

6ES79538LG200AA0

6ES79720BA120XA0

6ES79720CB200XA0

591C/1500/5/3/0/0/0/41/000

E32NRFP-LNN-NS-00

6MD6355-5EB22-0AA0

HOG10D 1024I 序列号:2025638

IC693CHS392

IC693CHS391

IC693CMM311

IC693ALG223

IC693ALG392

IC693CPU372

IC693MDL645

IC693MDL740

IC693PWR331

IC697ALG440

6DD1600-0AK0

183432B-01

1762-L40BWA

1305-BA03A-HA2

140CPS11420

140CPU53414A

140NOE71100

140XBP00600

170AAI14000

170AAO92100

170ADI34000

170ADO34000

170INT11000

171CCC96030

172JNN21032